🏗️ What is Synthesis? #

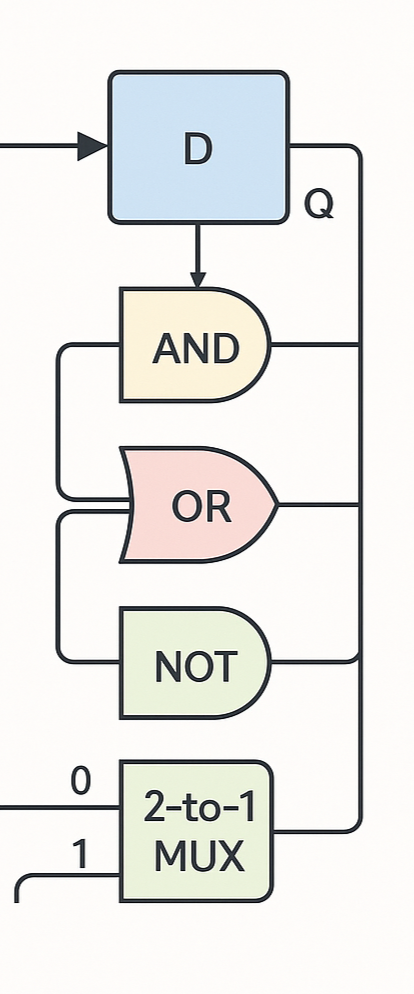

Synthesis is the process of transforming RTL Verilog code into a gate-level netlist that can be mapped onto physical hardware (FPGA or ASIC).

🔧 What happens during synthesis: #

- Converts

always/assignlogic into gates and flip-flops. - Resolves parameters and logic expressions.

- Applies optimization for area, speed, and power.

⚠️ Constructs to Avoid in Synthesizable Code #

| Construct | Why It’s Problematic | Use Instead |

|---|---|---|

initial block |

Not supported in synthesis | Use reset logic |

#delay |

Simulation-only delay | Use clocked always |

$display, $monitor |

Not synthesizable | Use in testbenches only |

for, while (variable bound) |

May not converge | Use generate with fixed range |

| Dynamic memory | Unsupported in hardware | Use fixed-size arrays |

🎨 How RTL Coding Style Affects Synthesis #

✅ Good Practices: #

- Use

always @(posedge clk)+<=(non-blocking) for sequential logic. - Use

always @(*)+=(blocking) for combinational logic. - Fully assign outputs to avoid unintended latches.

- Keep sensitivity lists complete or use

(*).

❌ Bad Practices: #

- Mixing

=and<=in the same block. - Partial assignments → inferred latches.

- Using simulation-only constructs in synthesizable code.

❗ Example: Unintended Latch Inference #

always @(*) begin

if (en)

y = a; // Latch inferred if en is false

end

✅ Corrected version:

always @(*) begin

if (en)

y = a;

else

y = 0;

end

🔁 Summary Table #

| Topic | Behavioral Sim | Gate-Level Sim | Synthesis |

|---|---|---|---|

| Simulation speed | Fast | Slow | N/A |

| RTL constructs | Allowed | Flattened | Synthesizable |

| Timing modeling | Approximate | Accurate | Deterministic |

| Usage | Functional test | Final verification | Netlist generation |

| Delay support | Yes (#) |

Yes (SDF) | No |