🧬 Verilog Veri Tipleri, Mantık Değerleri, Diziler ve Net Türleri#

Verilog, donanım davranışını hem simülasyon hem de sentez için modellemek amacıyla çeşitli veri türleri ve sinyal durumları sunar. Bu bölümde en yaygın türler, 4 durumlu simülasyonda mantığın nasıl çalıştığı ve dizilerle modül örneklerinin nasıl yapılandırıldığı açıklanır.

📦 Yaygın Verilog Veri Tipleri#

| Tür | Kategori | Signed? | Varsayılan Genişlik | Başlangıç Değeri | Kullanım Örneği |

|---|---|---|---|---|---|

wire | Net (kombinasyonel) | Hayır | 1 bit | x | Sürekli atama (assign) |

tri | Net (üç durumlu) | Hayır | 1 bit | z | Ortak veriyolu, tri-state |

wand | Wired-AND bağlantı | Hayır | 1 bit | x | Çoklu sürücülü AND bağlantısı |

wor | Wired-OR bağlantı | Hayır | 1 bit | x | Çoklu sürücülü OR bağlantısı |

reg | Değişken (procedural) | Hayır | 1 bit | x | always bloğunda kullanım |

integer | Değişken | Evet | 32 bit | 0 | Döngü sayaçları, hesaplamalar |

real | Değişken | Evet | 64 bit float | 0.0 | Sadece simülasyon matematiği |

time | Değişken | Hayır | 64 bit | 0 | Simülasyon zamanı takibi |

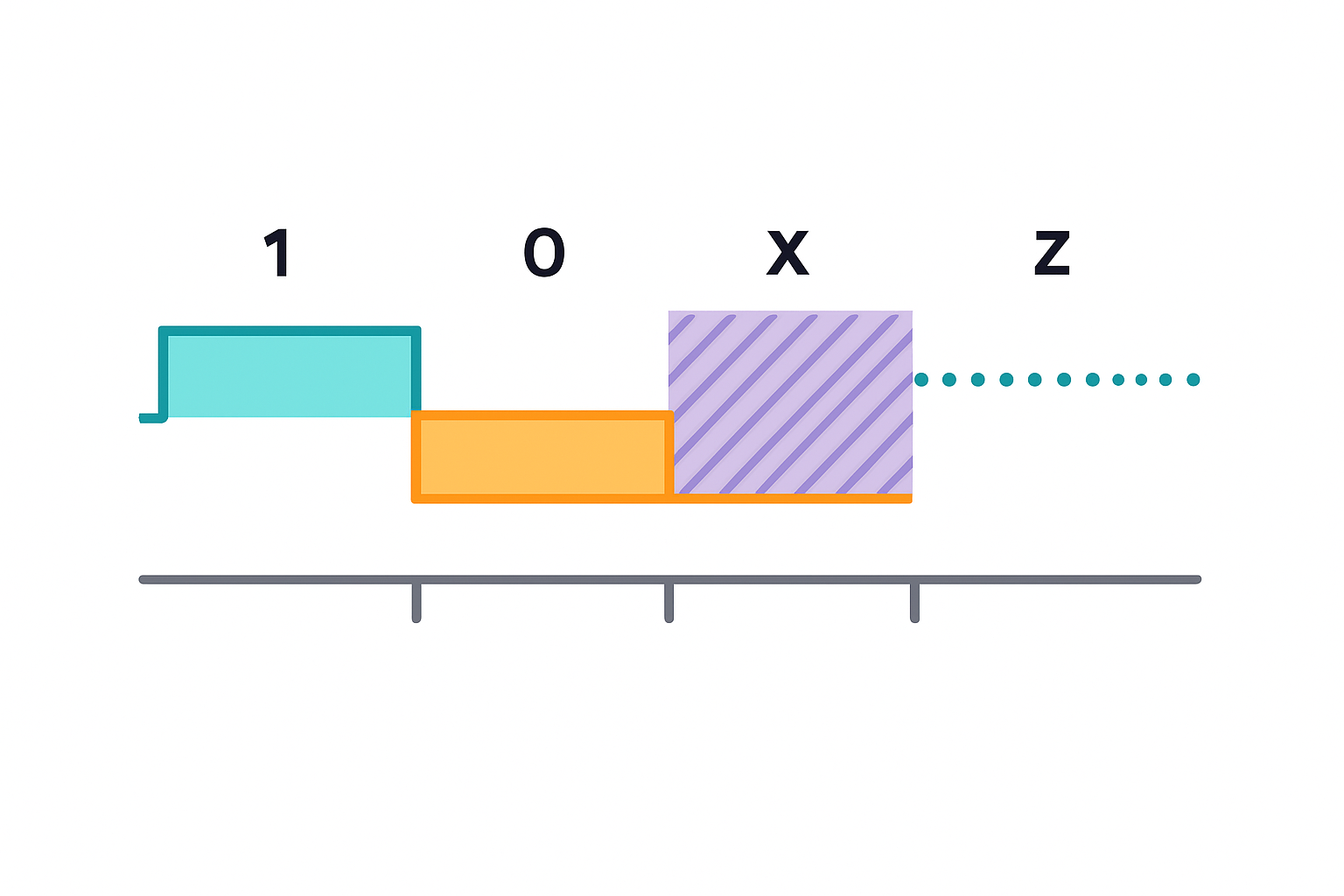

🔢 Verilog Mantık Değerleri#

Verilog, her bitin sadece 0 ve 1 dışında değerler de alabileceği 4 durumlu mantık sistemi kullanır:

| Değer | Adı | Anlamı |

|---|---|---|

0 | Mantık 0 | Sinyal düşük seviyeye sürülmüş (aktif 0) |

1 | Mantık 1 | Sinyal yüksek seviyeye sürülmüş (aktif 1) |

x | Bilinmeyen | Çakışma veya atanmamış değer |

z | Yüksek empedans | Sinyal sürülmemiş, boşta (ör. tri-state veriyolu) |

⚠️

xvezdurumları simülasyonda hataları tespit etmek ve veri yolu davranışını modellemek için kritik öneme sahiptir.

🧠 Örnek#

module tb_logic_values;

reg a = 1'b1;

reg b = 1'bz;

reg c = 1'bx;

reg d = 1'b0;

initial begin

$display("a = %b", a);

$display("b = %b", b);

$display("c = %b", c);

$display("d = %b", d);

end

endmodule

a: mantık 1b: yüksek empedans (sürülmemiş)c: bilinmeyen (çakışma veya başlangıçta atanmadı)d: mantık 0

📏 Scalar (Skaler) ve Vector (Vektör)#

🔹 Skaler#

- Tek bitlik sinyal

- Genişlik belirtilmezse varsayılan olarak skaler kabul edilir

wire enable; // 1-bit skaler sinyal

🔹 Vektör#

- Çok bitli sinyaldir, veriyolları veya gruplanmış veriler için kullanılır

wire [7:0] data_bus;

reg [3:0] nibble;

📚 Verilog’ta Diziler#

Diziler, sinyalleri, bellek yapıları, kayıt dosyaları ve çoklu modül örneklerini gruplamak için kullanılır.

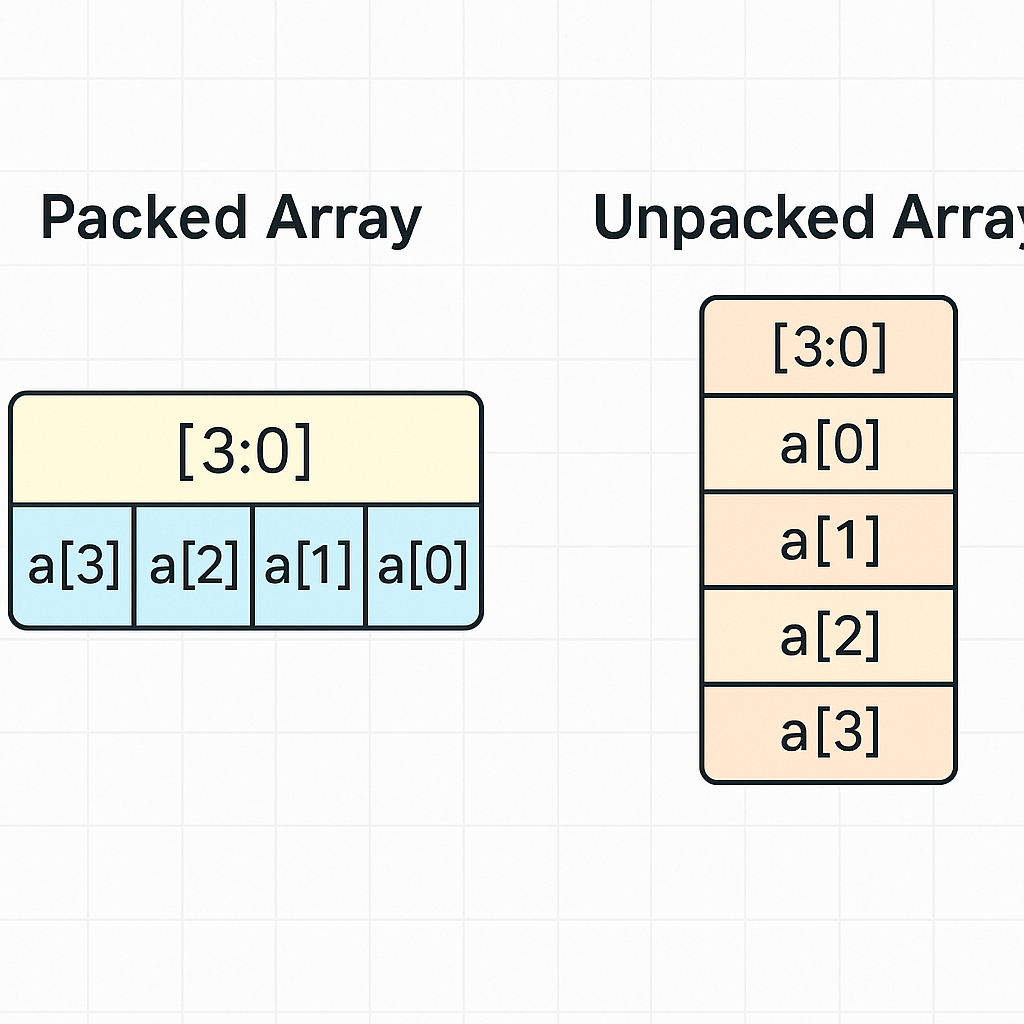

🔹 1. Packed Arrays (Bit-Vektörler)#

Sabit genişlikte bit gruplarını temsil eder.

reg [3:0] my_bus;

Örnek:#

module tb_bit_select;

reg [3:0] my_bus = 4'b1010;

initial begin

$display("Bit 2: %b", my_bus[2]); // Çıktı: 1

end

endmodule

🔹 2. Unpacked Arrays (Bellek Tarzı)#

RAM, ROM veya lookup table gibi yapıları modellemek için kullanılır.

reg [7:0] memory [0:255];

Örnek:#

module tb_memory_init;

reg [7:0] memory [0:3];

initial begin

memory[0] = 8'hFF;

memory[1] = 8'hA2;

$display("memory[0] = %h", memory[0]);

$display("memory[1] = %h", memory[1]);

end

endmodule

🔹 3. Çok Boyutlu Diziler#

Verilog-2001 ile desteklenmiştir. Genellikle resim verisi, matris veya önbellek yapıları için kullanılır.

reg [7:0] image [0:63][0:63]; // 64x64 piksel, her biri 8 bit

🔹 4. Döngü ile Dizi Başlatma#

module tb_memory_clear;

reg [7:0] memory [0:255];

integer i;

initial begin

for (i = 0; i < 256; i = i + 1)

memory[i] = 8'h00;

// Display first few entries for verification

$display("memory[0] = %h", memory[0]);

$display("memory[1] = %h", memory[1]);

$display("memory[255] = %h", memory[255]);

end

endmodule

🔹 5. Modül Örneklerinden Dizi Oluşturma#

generate yapısı ile tekrar eden donanım bloklarını instantiate edebilirsin:

module top_module (

input [3:0] in,

output [3:0] out

);

genvar i;

generate

for (i = 0; i < 4; i = i + 1) begin : gen_block

my_module u_inst (

.in(in[i]),

.out(out[i])

);

end

endgenerate

endmodule

module my_module (

input in,

output out

);

assign out = ~in;

endmodule

🔹 Vektör Bit Seçimi ve Parça Seçimi (Bit-Select ve Part-Select)#

Bir vektör sinyalinin tek bir bitine veya belirli bir bit aralığına erişmeyi sağlar.

module tb_select;

reg [7:0] a = 8'b1101_0110;

initial begin

$display("a = %b", a);

$display("a[3] = %b", a[3]); // Bit seçimi: 3. bite erişim

$display("a[7:4] = %b", a[7:4]); // Parça seçimi: 7'den 4'e kadar olan bitlere erişim

end

endmodule

Özellikle veri yolları (bus) ve register’ların belirli bölümlerini işlemek için kullanılır.

🔹 Atamalar ve Truncation (Kesilme)#

Farklı genişlikteki vektörler arasında atama yapıldığında:

- Daha geniş vektöre atama yapılırsa, eksik bitler sıfır ile doldurulur (zero-padding).

- Daha dar vektöre atama yapılırsa, fazla bitler kesilir (truncation).

module tb_truncation_padding;

reg [7:0] a;

reg [3:0] b;

initial begin

b = 4'b1011;

a = b; // 4 bitlik `b`, sıfırla doldurularak 8 bite tamamlanır

$display("a = %b", a); // Expected: 00001011

a = 8'b11011010;

b = a; // 8 bitlik `a`, alt 4 biti alınarak `b`'ye atanır

$display("b = %b", b); // Expected: 1010

end

endmodule

⚠️ Truncation dikkatli kullanılmalıdır; veri kaybına neden olabilir.

🎯 Dizi Türleri Özeti#

| Dizi Türü | Açıklama | Kullanım Alanı |

|---|---|---|

| Packed Array | Bit-vektörler | Portlar, veriyolları, mantık |

| Unpacked Array | Elemanların indeksli saklanması | RAM, kayıt dosyaları |

| Multidimensional Array | Matris şeklinde veri yapıları | Görüntü, önbellek, LUT |

| Array of Instances | Çoklu modül örneklemesi | Paralel/pipeline yapılar |