🧠 Donanım Tasarım (Soyutlama) Seviyeleri#

Donanım tasarımı, farklı detay seviyelerinde yapılabilir. En üst seviyede sistemin genel çalışması tanımlanırken, en alt seviyede transistörlerin nasıl bağlandığı gösterilir.

1️⃣ Mimari Seviye (En Üst)#

- Ne yapar?: Sistemin genel özelliklerini tanımlar

- Örnekler:

- “32-bit işlemci tasarlanacak”

- “1MB cache kullanılacak”

2️⃣ RTL (Register Transfer Level)#

- Ne yapar?: Verinin registerlar arasında nasıl hareket ettiğini tanımlar

- Örnek Verilog:

module counter(

input clk,

output reg [3:0] count

);

always @(posedge clk)

count <= count + 1;

endmodule

3️⃣ Kapı Seviyesi#

- Ne yapar?: Mantık kapıları (AND, OR, NOT) ve bağlantıları gösterir

- Örnek:

module top_module (

input a,

input b,

input d,

input clk,

output out,

output q

);

AND2X1 U1 (

.A(a),

.B(b),

.Y(out)

);

DFF U2 (

.D(d),

.CLK(clk),

.Q(q)

);

endmodule

module AND2X1 (

input A,

input B,

output Y

);

assign Y = A & B;

endmodule

module DFF (

input D,

input CLK,

output Q

);

reg Q_reg;

assign Q = Q_reg;

always @(posedge CLK) begin

Q_reg <= D;

end

endmodule

4️⃣ Transistör Seviyesi#

- Ne yapar?: Transistörlerin nasıl bağlandığını gösterir

- Kullanım: Özel devreler (bellek hücreleri gibi) için

- Örnek: CMOS inverter tasarımı

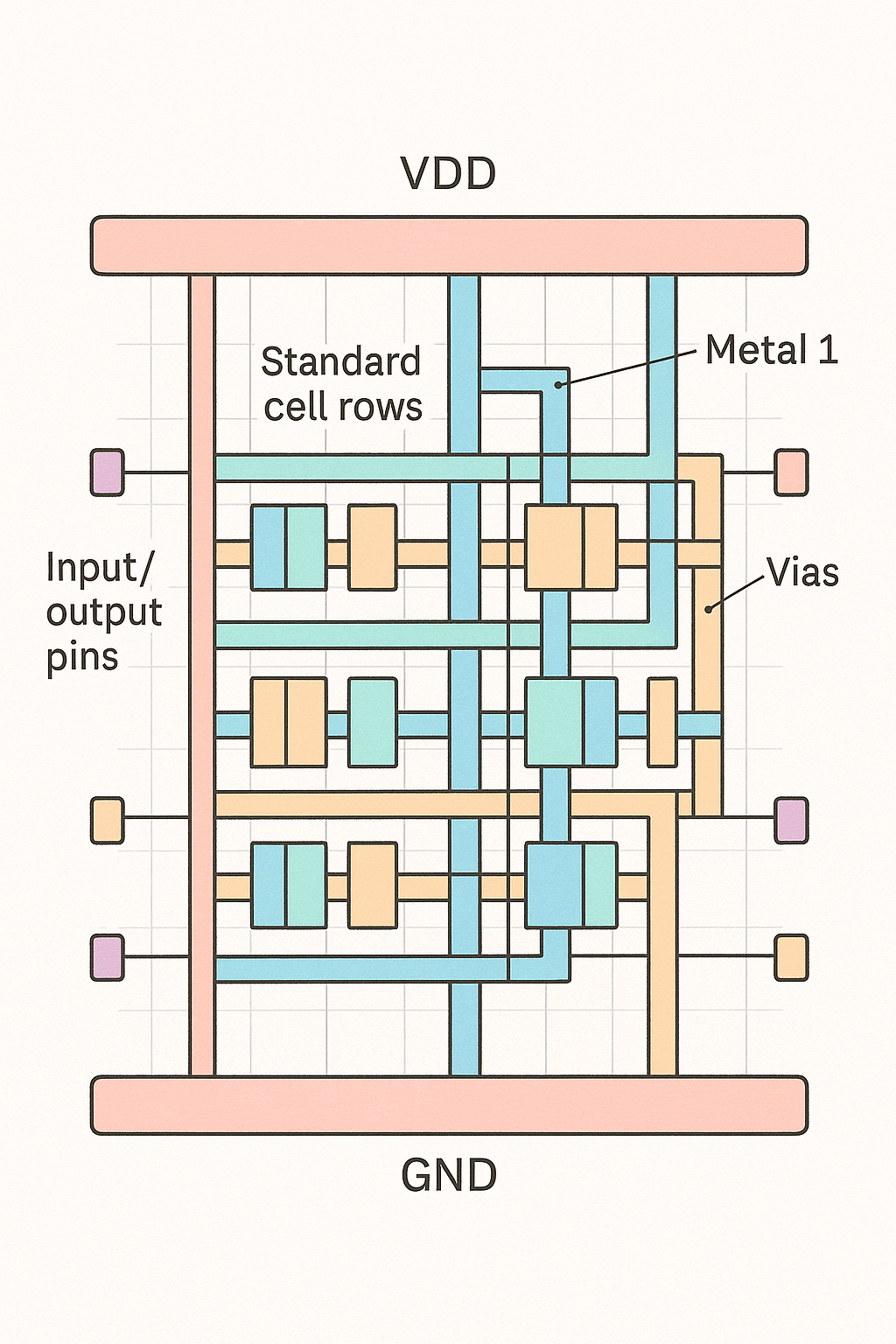

5️⃣ Fiziksel Yerleşim (En Alt)#

- Ne yapar?: Çip üzerinde bileşenlerin fiziksel konumunu belirler

- Çıktı: GDSII dosyası (üretim için)