🔧 Verilog Nedir?#

Verilog, dijital elektronik sistemleri tanımlamak, simüle etmek ve gerçeklemek için geliştirilmiş bir Donanım Tanımlama Dili (HDL)’dir. Basit mantık kapılarından karmaşık işlemcilere kadar her seviyedeki devreyi tanımlayabilmeni sağlar.

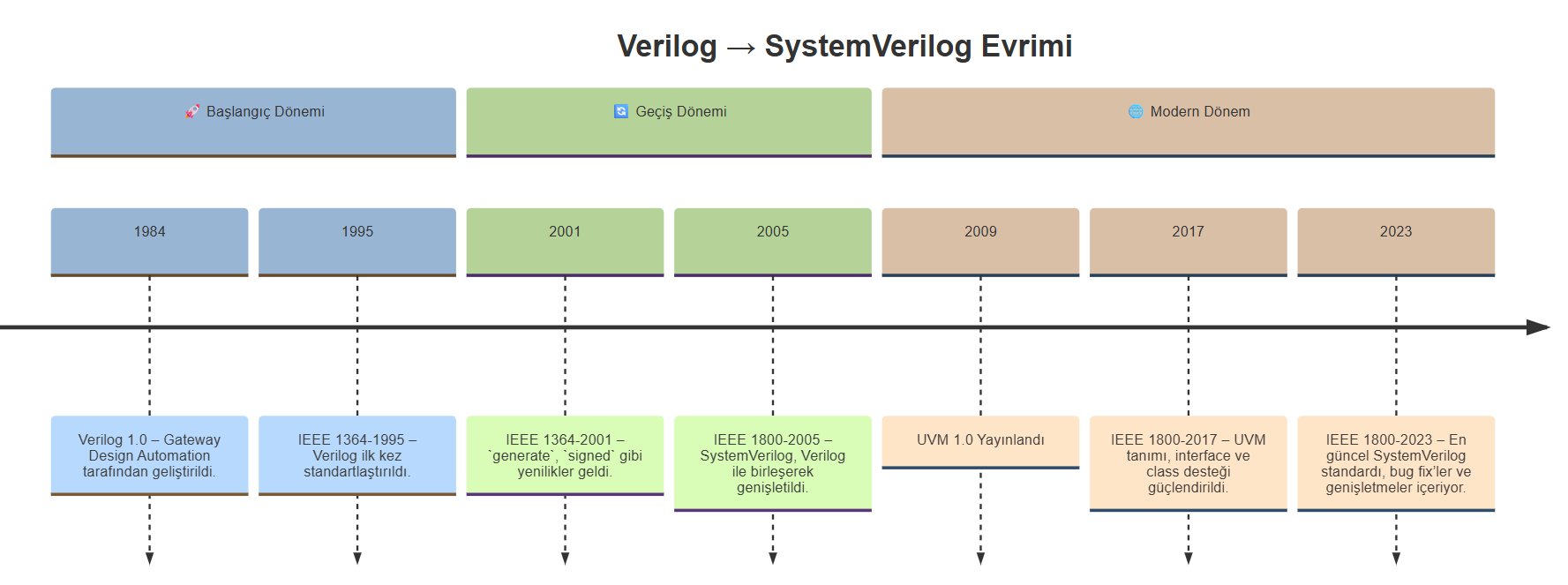

1980’lerde Gateway Design Automation tarafından geliştirilen Verilog, daha sonra IEEE tarafından IEEE 1364 standardı olarak kabul edilmiştir. Verilog, donanımı programlama benzeri bir sözdizimiyle metin tabanlı olarak tanımlamana olanak tanır.

Verilog, geleneksel yazılım dillerinden farklı olarak CPU üzerinde çalışmaz. Bunun yerine, tanımlanan devreler FPGA veya ASIC gibi fiziksel donanımlara sentezlenerek yüklenir. Verilog ile aşağıdaki donanım yapılarını modelleyebilirsin:

- Mantık kapıları ve kombinasyonel devreler

- Sıralı devreler (flip-flop’lar, register’lar)

- Durum makineleri

- Tam işlemci mimarileri

🕰️ Verilog’dan Önce Ne Vardı?#

Verilog’dan önce dijital donanım genellikle şematik giriş araçları veya çok düşük seviyeli tanımlama dilleriyle tasarlanıyordu. Bunlara örnek:

- Anahtar seviyesi modelleme veya transistör düzeyinde şemalar – devreler kapı kapı ya da transistör transistör tanımlanırdı.

- ABEL (Advanced Boolean Expression Language) – 1980’lerin başında PAL ve CPLD’ler için kullanıldı.

- PALASM (Programmable Array Logic Assembler) – PAL cihazları için mantık denklemlerini tanımlayan ilk donanım dillerindendir.

- VHDL (VHSIC Hardware Description Language) – 1981’de ABD Savunma Bakanlığı tarafından geliştirilmiş, 1987’de IEEE 1076 olarak standartlaşmıştır.

Not: VHDL daha ayrıntılı ve sıkı kurallara sahipken, Verilog daha sade ve C benzeri bir yapıyla özellikle RTL modellemede kullanıcı dostu bir alternatif sunmuştur.

🚀 Verilog Ne Getirdi?#

Verilog, daha önceki HDL’lere ve şematik tabanlı tasarımlara kıyasla donanım tasarımını daha okunabilir ve erişilebilir hale getiren C-benzeri bir sözdizimi sundu.

Verilog’un başlıca katkıları:

- ✅ RTL Modelleme:

always,assignveinitialblokları ile register transfer seviyesinde (RTL) sadeleştirilmiş tanımlama - ✅ Karışık Soyutlama: Hem davranışsal hem de kapı seviyesinde tanımlamayı destekler

- ✅ Modüler Tasarım: Modül tabanlı hiyerarşik yapıyı destekler, tekrar kullanılabilirliği artırır

- ✅ Geniş Araç Desteği: Sentezle uyumlu yapısı sayesinde endüstride hızla yaygınlaşmıştır

💻 HDL (Donanım Tanımlama Dili) Nedir?#

HDL, dijital devrelerin davranışını ve yapısını modellemek için kullanılan programlama benzeri dillerdir. En yaygın HDL’ler Verilog ve VHDL’dir.

Yazılım dillerinden farkı, HDL kodunun gerçek donanıma sentezlenmek üzere yazılmasıdır. Yani yazılan kod, FPGA ya da ASIC’e dönüştürülerek fiziksel bir devre haline gelir.

🧠 HDL ve Yazılım Dilleri: Verilog Neden Farklıdır?#

İlk bakışta Verilog, bir programlama diline benzer: if, case, for gibi yapılar ve noktalı virgüller kullanır. Ancak gerçek şu ki, Verilog bir yazılım dili değildir.

İşte Verilog gibi HDL’lerin C, Java veya Python gibi geleneksel yazılım dillerinden nasıl ayrıldığı:

| Özellik | Verilog (HDL) | C / Python / Java (Yazılım) |

|---|---|---|

| Çalışma Modeli | Olay tabanlı, paralel çalışır | Talimat tabanlı, sıralı çalışır |

| Zaman Bilinci | Açıktır (#10, @posedge) | Zaman belirsizdir veya yoktur |

| Çıktı Davranışı | Donanım bağlantılarını tanımlar | Yazılımsal davranışları hesaplar |

| Eşzamanlılık | Birden fazla blok aynı anda çalışır | Kod satır satır çalışır |

| Nihai Hedef | Fiziksel donanım (FPGA/ASIC)’e çevrilir | CPU veya sanal makinelerde çalışır |

Verilog gerçek dünyadaki devreleri simüle eder. Sadece “çalışmaz” — olayları bekler, sinyal değişikliklerine tepki verir, ve fiziksel zamanlamayı modellemeye odaklanır.

Bu olay tabanlı doğa, Verilog’u güçlü kılan temel farktır. Örneğin:

module incrementer (

input clk,

input [7:0] data_in,

output [7:0] data_out

);

reg [7:0] data_out_reg;

assign data_out = data_out_reg;

always @(posedge clk) begin

data_out_reg <= data_in + 1;

end

endmodule

Bu blok yalnızca clk sinyalinde yükselen kenar oluştuğunda tetiklenir; yazılım gibi sırayla çalışmaz. Bu nedenle, zaman, gecikme ve sinyal hassasiyeti HDL tasarımı için kritik kavramlardır.

⚡ Yazılım ve Donanım Mantığı: Basit Bir Karşılaştırma#

Verilog öğrenirken, yazılımın sıralı yapısı ile donanımın eşzamanlı tanımı arasındaki farkı kavramak çok önemlidir.

👨💻 Yazılım Tarafı (C kodu – sıralı)#

int a = 5;

int b = a + 3;

C’de CPU bu satırları sırasıyla çalıştırır: önce a = 5 atanır, sonra b = a + 3 hesaplanır ve b’ye atanır. Bu değerler daha sonra açıkça değiştirilmedikçe sabit kalır.

🔌 Donanım Tarafı (Verilog – eşzamanlı)#

assign b = a + 3;

Verilog’da bu bir tek seferlik işlem değildir. Aksine bu, sürekli aktif bir tanımlamadır:

aher değiştiğinde,banında ve otomatik olarak güncellenir — sanki bir tel ikisini bağlıyormuş gibi.

Burada talimat sırası yoktur. Sadece sinyal akışı vardır — gerçek donanım davranışına benzer şekilde.

💡 Yeni Başlayanlar İçin Tavsiyeler#

Verilog’u C veya Python gibi düşünme. Bunun yerine:

- Donanım yapısını düşün, yazılım akışını değil.

- Kendine şu soruyu sor: “Gerçek donanımda nasıl bir yapı tanımlıyorum?”

- Zaman, kenar ve sinyal bağımlılığı kavramlarını öğren ve özümse.

Bu zihinsel dönüşüm, Verilog ile etkili tasarımlar yapmanın anahtarıdır.